Étude de la sensibilité des System-on-Chip aux attaques par illumination laser

Sujet de Thèse

Description

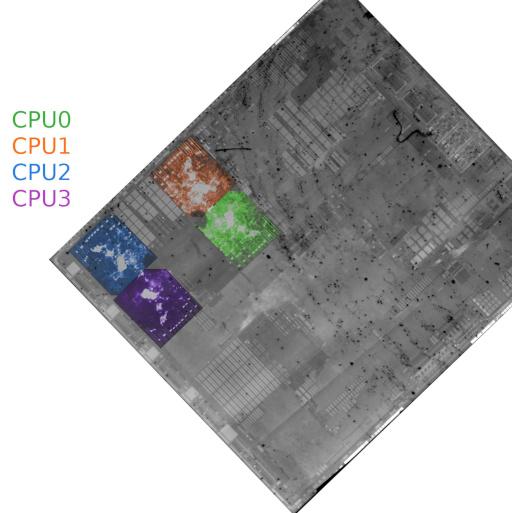

L’objectif de cette thèse sera d’étudier le potentiel des attaques par illumination laser pour extraire des secrets cryptographiques ou contourner un mécanisme de sécurité. En effet, les photocourants induis par l’illumination laser du silicium d’un circuit peut mener à la perturbation de celui-ci. Les cibles étudiées seront des System-on-Chip (SoC) du type de ceux utilisés dans des téléphones mobiles.

Des travaux de l’équipe SAS ont permis de montrer que d’autres types d’attaques comme l’injection de fautes par perturbation électromagnétique permettent de contourner des mécanismes de sécurité sur un System-on-Chip [1]. Pour les attaques par illumination laser, il a été démontré dans la littérature que, dans certaines situations, elles peuvent permettre de contourner des mécanismes de sécurité sur ces cibles [2]. Néanmoins, les phénomènes mis en jeu et la complexité de la micro-architecture de ce type de cibles rend le contrôle de la faute injectée par l’attaquant difficile [3].

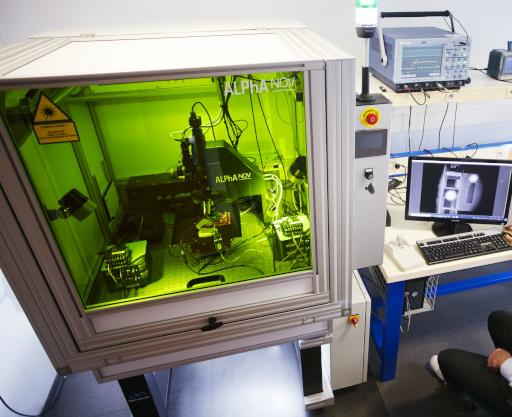

Dans un premier temps, le doctorant ou la doctorante explorera de nouvelles méthodes pour optimiser l’injection de fautes par illumination laser sur System-On-Chip (ex: conception d’un code sous attaque maximisant l’observabilité d’apparition d’erreurs dans l’exécution de celui-ci, imagerie, photo-émission, défocalisation, exploration exploitant deux spots lasers…). Dans un second temps, les travaux de thèse viseront à étudier l’impact de la technologie et du noeud technologiquedu circuit cible sur la faisabilité de ce type d’attaque. Dans un troisième temps, les travaux se concentreront sur le developpement de nouvelles méthodes pour contourner des verrous spécifiques à l’injection de fautes par illumination laser dans un System-on-Chip.

Les laboratoires LSCO (Laboratoire de Sécurité des COmposants) et LTSO (Laboratoire de Tests de Sécurité & Outils) accueilleront le/la doctorante sur son site de Gardanne au sein de l’équipe de recherche commune entre le CEA et l’MSE: SAS “Systèmes et Architectures Sécurisés”. Cette équipe dispose d’équipements de pointe avec des bancs d’attaque physique au niveau de l’état de l’art international. Elle est située entre Aix-En-Povence et Marseille à Gardanne sur le campus Aix-Marseille Provence. La thèse sera co-dirigée par Jean-Max Dutertre (MSE) et Jessy Clédière (CESTI-Leti) et co-encadrée par Simon Pontié (CEA) et Driss Aboulkassimi (CEA).

Plus d’informations:

- https://www.simon.pontie.fr/sujet-these/laser-soc/index.html

- https://www.simon.pontie.fr/

- https://www.emse.fr/~dutertre/

- https://www.leti-cea.fr/cea-tech/leti/Pages/innovation-industrielle/innover-avec-le-Leti/CESTI.aspx

- https://www.leti-cea.fr/

- https://instn.cea.fr/these/etude-de-la-sensibilite-des-system-on-chip-aux-attaques-par-illumination-laser/

- https://www.abg.asso.fr/fr/candidatOffres/show/id_offre/119067/job/etude-de-la-sensibilite-des-system-on-chip-aux-attaques-par-illumination-laser-laser-fault-injection-exploration-on-system-on-chip

Profil recherché

Le candidat/La candidate pourra avoir suivi un cursus Mathématique, Informatique, Électronique ou micro-électronique. Une expérience en lien avec l’analyse de vulnérabilités matérielles n’étant pas obligatoire, mais appréciable.

La thèse démarrera début octobre 2024.

Candidature

Les candidatures sont fermées.